加法器[]

第一個版本[]

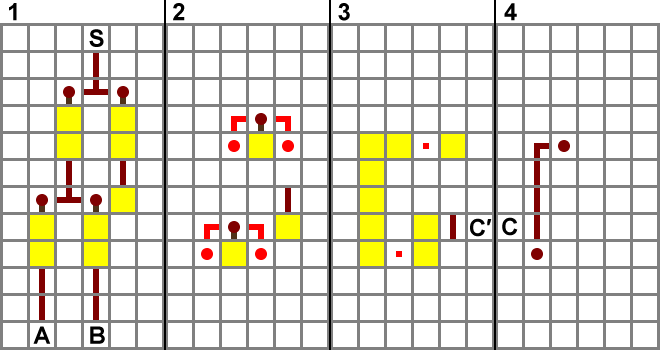

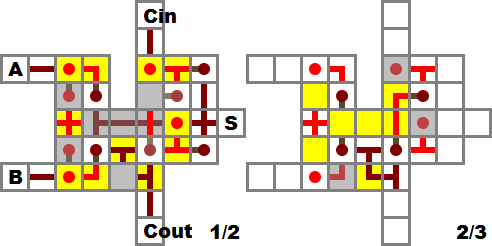

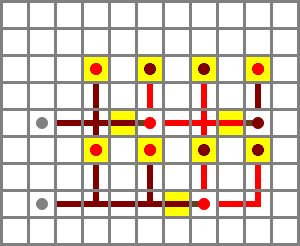

全加器的遊戲截圖

- 全加器

一個全加器接受兩個輸入位A、B以及一個來自低位的進位,並輸出一位和以及向高位的進位。它依賴於2個異或門,2個與門和1個或門。經過一些方面的考慮後,這些邏輯門結構可以被壓縮

如圖,A、B是兩個輸入位且C'是來自低位的進位。它產生一個和(S)以及向高位的進位(C)。當多個全加器單元連接在一起時,將下一個全加器的C'和目前全加器的C連接起來,以便產生的進位能夠向高位傳遞。

- 半加器

半加器和全加器幾乎相同,但沒有第二個異或門並且直接從第一個異或門輸出和(S)。它沒有來自低位的進位(C'),但向高位的進位(C)仍然在第一個異或門頂端且向第一個全加器產生一個進位。有的運算器不使用半加器作為第一位,以支援增量(允許向第一位進位)。

單列版加法器[]

- 全加器

2格寬全加器的遊戲截圖

這種全加器相似於上面的那種,除了事實上它兩格寬且易於對齊。這樣的設計對於最小化水平空間是相當有用的,而且可以被成列地建造並接入兩條紅石總線,消除因擴張總線以接入擴大規模的加法器(的要求)致浪費的空間。

| 教學影片(在 YouTube 上觀看) |

|---|

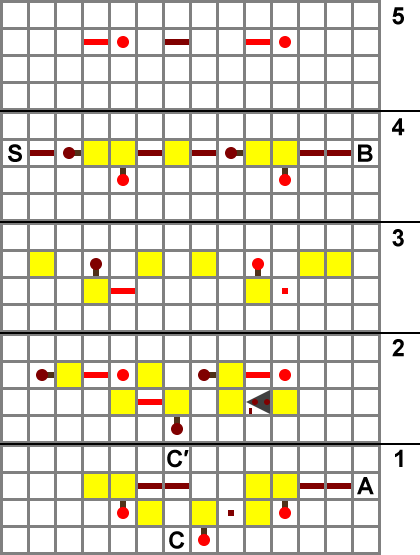

第二個版本[]

- 全加器

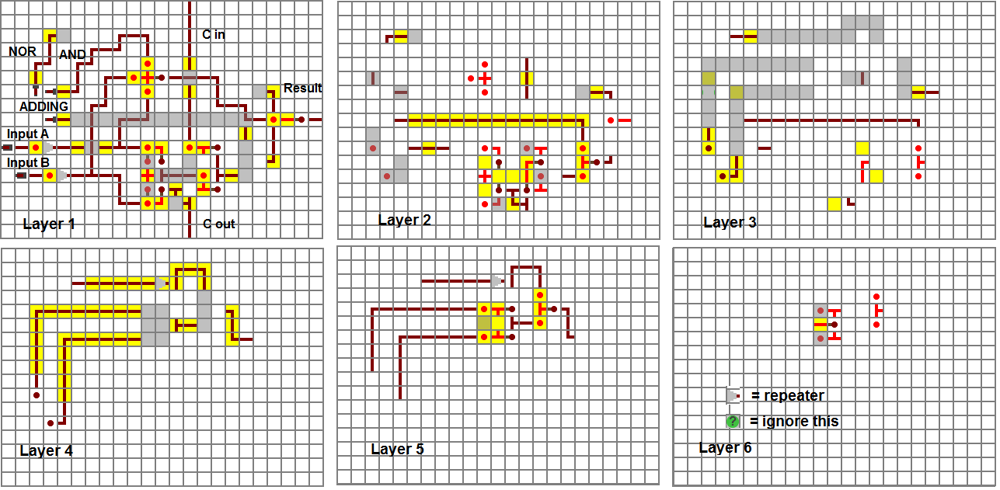

使用的邏輯門:同或門(2),蘊涵門,非門,或門,與門

尺寸:6×12×5(包括輸入輸出訊號佔用的空間)

這個加法器將取2個輸入位A、B和1個低位的進位C(事實上是C的否定C而並非是C,即示意圖中Layer 1左下角紅石端的訊號值)並將它們相加,產生一個和位(S)和一個向高位的進位(這裏同樣是C的否定C而並非是C)。

使用上述的邏輯門時,請注意輸入和輸出。你可能想知道為什麼有那麼多反相的訊號位用以代替常規的訊號位。

上述加法器使用了同或門而不是異或門,因為這樣設計更加緊湊。同理,我們使用蘊含門來代替與門,這樣能夠更加緊湊。

因此對於(結構)最緊湊的加法器,必然要使用反相的訊號。這些加法器太複雜,很難用(每格可以容納2層的)平面圖來表示,所以將每一層都單獨表示為一張示意圖以使建造過程更加清晰易懂。

- 半加器

使用的邏輯門:同或門,蘊含門

尺寸:5×4×4

這個加法器將2個輸入位相加得到結果作為和輸出(S)。如果2個輸入位的訊號值都是1,進位C將會得到1(C將會是0)。可以對這個半加器進行修改來獲得一個非反相的輸出C,但使用這個半加器才能作為一個全加器鏈(多位全加器)的起始部分。

拓展: 對於剛接觸紅石的人來説,這樣更容易理解:我們説輸出位C有一個非門將訊號反相併連接到一個鐵門、活塞門之類的門,輸出位S連接到一些黏性活塞來控制地面陷阱。假設有一個1×1×1的方塊不受黏性活塞影響,稱之為安全方塊。當輸入位A有紅石訊號時,門打開的同時,地面也會打開,如果你站在安全方塊上,你就不會掉下去。輸入位B只控制地面,但如果輸入位A有紅石訊號,則輸入位B會同時控制這二者。(同理)當兩個輸入位都有紅石訊號時,輸入位A只控制地面。這意味着如果你離開伺服器的時候不想讓任何人進來,你可以給輸入位A和B加上紅石訊號,當其他人移除輸入位A的紅石訊號時,地面會打開,但門依然是關閉的。即使他們知道這個祕密也仍然不能進來。

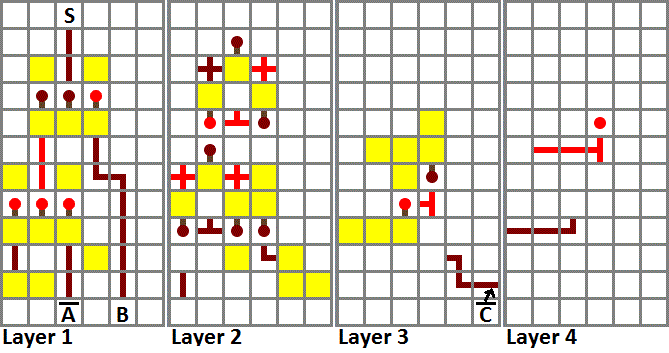

第三個版本[]

- 全加器

尺寸:5×6×3

每位進位都是相互對齊的,這樣可以方便地串聯這些子模組。

快速加法器[]

當建造高級數字電路比如計算機和乘法器時,使用的加法器必須儘可能地快,以確保最大的執行速度。簡單的加法器存在一個基本的速度問題,許多加法器設計都嘗試改善這一問題。這個問題是進位傳播的延遲,這是由加法器的進位方式所引起的延遲。我們可以看如下的1111 + 0001的例子:

1111 0001 ---- 1110

這是加法運算過程的第一步,對兩個輸入異或。由於最低有效位有兩個1,這會觸發與門產生進位並送往高位:

1 1111 0001 ---- 1100

此時就產生了問題:由於待進位的目前位上仍然有兩個1,所以會再次觸發向高位的進位。這是透過將第一個半加器的輸出與低位的進位相加來完成的,這裏存在很大的問題,因為接下來你將反覆產生向高位的進位直到越過最高位。如果每個與門產生2刻的延遲,為了計算最後一步中需要相加的所有進位,總共需要2刻×4,即8刻的時間。

如果現在你要計算999+1,你不會有「9 + 1 = 10,進位1,所以9 + 1 = 10,進位1,所以9 + 1 = 10,得到1000」這種閒得無聊的想法。在高級電路中同樣也是如此。

真正的電路工程師和有創造力的紅石玩家已經設計出了計算進位比這種串行方式更高效的電路。

順便提一下,以這種串行方式計算進位的加法器被稱為行波進位加法器。

活塞加法器[]

解決行波進位存在的問題的最簡單、最經典的方法之一是使用帶活塞的即時與門。這種加法器簡單快速,但由於使用活塞導致電路不穩定,當方塊因意外而跌落時,整個電路就被破壞了。活塞也存在時鐘同步上可能難以忍受的不便之處,在建造高級電路時可能會對(整個裝置)的同步時鐘產生嚴重依賴性。

每當產生進位時,其將會透過帶拉桿的紅石線路傳送,而不是與門。活塞收縮,進位C被送到高位,這一過程完全沒有產生進位傳播的延遲(直到訊號強度耗盡)。

下面這個影片展示了這種邏輯的一個簡單實現。這種設計龐大而且分散,容易看到每一個單獨的加法器部分以及進位邏輯。

| YouTube影片(在 YouTube 上觀看) |

|---|

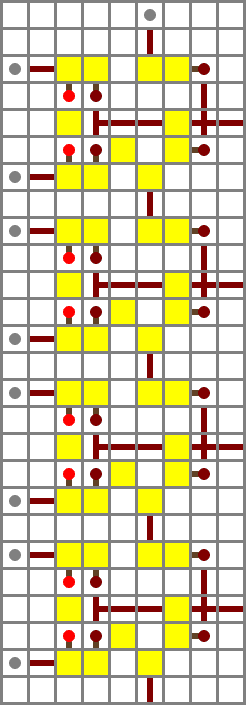

4位加法器[]

使用的邏輯門:同或門(7),蘊含門(4)非門(4),或門(3),與門(3)

尺寸:23×12×5

注意!最低有效位(個位)在圖的左邊,這樣可以更清楚地看到從半加器到全加器的過程。如果想要通常的從左向右的輸入,請翻轉示意圖。

這個加法器將第2、第4位的輸入位(A和B)相加,每加1位產生一個和(S)以及一個進位(C)。和的順序與輸入位順序相同,這意味着圖中最左邊的輸出位S代表連接嘅最低有效位。這是一個多位加法器的例子;加法器可以透過這種方式串聯起來以計算更多位數的數字。

交替式4位加法器[]

功能相同但設計不同,使用4個全加器而不是1個半加器和3個全加器。

注意:開關為輸入位A和B(頂部為低位進位C)。

減法器[]

減法和加法的道理是一樣的,例如,3 - 2 = 3 + (-2) = 1。因為我們已經有了加法計算的框架,只需要加入一個負號就可以簡單地得到結果。問題在於如何表示這個負數。

我們對小學減法中向高位借位的概念很熟悉,比如這樣:

5623 - 128 -----

我們沒有辦法用3減去8,所以我們從高一位借了1以透過13減8代替(結果顯然是5)。

1

5623

- 128

-----

5

然而計算機是沒法做這種考慮的,所以當計算機找到一個負數時,它不會也不能在前面硬添一個負號。它只會像如下這樣從高位進行"借位"相減:

000000 - 3 ------- -999997

這在二進制中同樣適用。讓我們用一個4位二進制數作為例子:

1 11 111 1111 0000 0000 0000 0000 -0011 -0011 -0011 -0011 ----- ----- ----- ----- - 1 - 01 - 101 -1101

我們可以按照這個方式一直反覆計算下去,但這並沒有什麼用。這就體現了4位寄存器的作用:它將在接收到4位數據後截斷(拋棄其他數據)。因此,在我們截斷這個數字之後(在這個例子中已經得到了體現,否則最後連接嘅左邊會有無窮多個1),多虧這個小技巧,我們可以對這4位數據之外的0做任何想做的事情,包括在它們之前添一個1(這將在之後被證明是非常有用的)。

10000 -0011 ----- 1101 <-- 注意:这个数字是正数!成功!

還記得我們説過我們的紅石沒有特別的方法來區分正數和負數嗎?我們只是創造了一種區分的方式:如果數字的符號位(最高位)是1,那麼它就是一個負數。這種利用在二進制數中的小技巧其實是一套名為「二進制補碼」的理論。

二進制補碼的正式定義是:

一個負數b的補碼等於2 ^ (n+1) - b,其中n是b的位數。

本質上説,-b的補碼就是將b的補碼的各位取反(用1替換0,用0替換1)再加1。

我們所做的是將最高位變成一個"負號"(如果它是1),但如果你一直在閱讀這個頁面,你會意識到這沒有那麼簡單。通常把帶有這種符號標識位的數字稱為帶符號的整數。 在普通的加法器中,這種二進制補碼規則並不生效,這種數字稱為無符號的整數。無符號的數字可以比帶符號的數字取到更大的值,但不能比0小;帶符號的數字最大只能取到無符號數字所能取到的大約一半,但可以比0小。 這意味着這兩種數字有相同長度的取值範圍,但取值區間的位置不同,比如下面的8位元整數的例子:

无符号:0-255带符号:-128-127

應當注意的是,當使用最小的有符號數(在上面的例子中是-128)時,可能會出現一些匪夷所思的問題,所以應該避免這種情況。

現在我們有了一種用正的值來表示負數的方法,將它運用到加法器中就很簡單了。目前我們可以計算

A + B

我們要計算的是

A - B

即

A + (-B)

所以,只要我們輸入B的補碼,加法器就變成了減法器。透過使用符號位(最高位)作為進位的1,這很容易實現。剩下的就是如何對B求補碼。

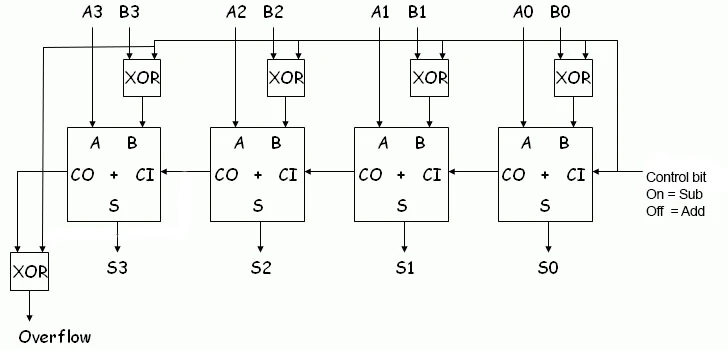

在實現此功能時需要注意一件重要的事情:因為得到的結果依然是二進制補碼,所以存在減去符號位的問題,因此要倒過來減。這個問題通常由最高位的加法器來處理。

這都可以實現到一個加法器中:

電路中加入了一個控制位,當它被通入紅石訊號時,就會變成一個減法器,當沒有紅石訊號時則是一個加法器。此外,在控制位和輸入B的每一位之間都增加了一個異或門,將每個異或門的輸出作為每個加法器單元真正的輸入位B。最後,為了使二進制補碼單元相容,需要在控制位和符號位上加入最後一個異或門。

這是在CPU中實現負數和減法的最簡單方法,因為它可以優雅地進行加法運算並將結果儲存在寄存器中。如果需要在計算器中實現這種操作,只需要將輸出結果減1,然後將符號位之外的每一位取反。如果數字是負數,只需要將符號位設為1即可。

為了建造一個減法器,只需要對其中一個輸入按位取反即可。如果這個數是負數,那麼結果也是相反的。在實際的計算機中,符號位決定數字的正負性,如果將它也納入考慮(應用相同的取反規則),你可以判斷出這到底是一個負數,還是僅僅是一個較大的數字。

邏輯單元[]

在電路中使用一個邏輯單元可能是有用的。邏輯單元會根據控制訊號來決定輸出哪種操作的結果。這樣的邏輯單元可以使用在更加複雜的電路中,比如ALU(算術邏輯單元)。

這是一個2位邏輯單元的例子,它的控制訊號有4種狀態。

它的輸出在最上面一行,從左到右依次透過輸入11、00、01和10來觸發(輸入在左邊,上面是低位,下面是高位)

以下是另一個使用格雷碼的簡化版本,輸出體現在最上面一行紅石火炬的亮滅。這種設計可以擴展到任意的位數,但考慮到時間效率的問題,一般不會超過1個字節(8位元)。輸出從左到右依次透過輸入11、01、00、10來觸發。

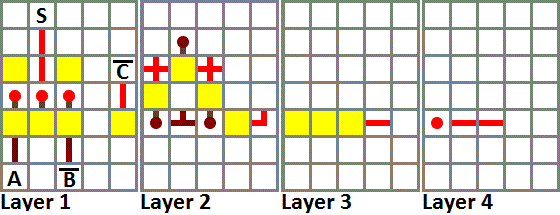

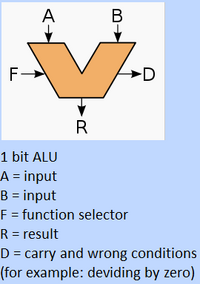

算術邏輯單元(ALU)[]

算術邏輯單元(ALU)是CPU的核心部分。它進行計算和邏輯處理,然後將結果傳遞給寄存器。ALU根據輸入來選擇一個特定的運算操作,執行它,然後給出結果。

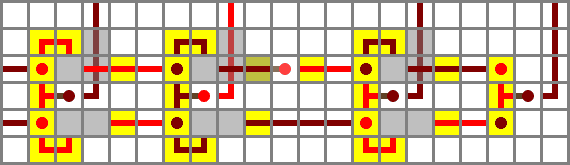

下圖顯示的ALU是一個1位的ALU,可以執行下列運算:ADD(求和),AND(求與),XOR(求異或)。它接收輸入A和B,然後執行所選擇的運算操作。閱讀加法器以了解ADD運算是如何工作的。XOR和AND運算是在邏輯電路頁面上所介紹的基本功能。

可以向ALU中加入更多的運算操作,比如乘法,除法,OR(求或),NAND(求與非)等等,這些運算都可以透過對ALU進行一定的修改來加入到其中。

這樣的1位ALU可以相互連接起來以形成多位的ALU。就像加法器一樣,把示意圖中的C out端連接到另一個ALU的C in端即可。

這是一個Minecraft中實際建造的1位ALU的遊戲截圖。你可以在這裏查看它的3D示意

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

語言